- 您现在的位置:买卖IC网 > Sheet目录350 > PCF8598C-2P/02,112 (NXP Semiconductors)IC EEPROM 8KBIT 100KHZ 8DIP

�� �

�

Philips� Semiconductors�

�PCF8598C-2�

�1024� � 8-bit� CMOS� EEPROM� with� I� 2� C-bus� interface�

�acknowledge�

�from� slave�

�acknowledge�

�from� slave�

�acknowledge�

�from� slave�

�acknowledge�

�from� slave�

�S�

�SLAVE� ADDRESS�

�0� A�

�WORD� ADDRESS�

�A�

�DATA�

�A�

�DATA�

�A�

�P�

�R/W�

�auto� increment�

�word� address�

�auto� increment�

�word� address�

�MBA701�

�Fig� 5.� Auto-increment� memory� word� address;� two� byte� write.�

�Page� write:� The� PCF8598C-2� is� capable� of� an� eight-byte� page� write� operation.� It� is�

�initiated� in� the� same� manner� as� the� byte� write� operation.� The� master� can� transit� eight�

�data� bytes� within� one� transmission.� After� receipt� of� each� byte,� the� PCF8598C-2� will�

�respond� with� an� acknowledge.� The� typical� E/W� time� in� this� mode� is�

�9� � 3.5� ms� =� 31.5� ms.� Erasing� a� block� of� 8� bytes� in� page� mode� takes� typical� 3.5� ms�

�and� sequential� writing� of� these� 8� bytes� another� typical� 28� ms.�

�After� the� receipt� of� each� data� byte,� the� three� low-order� bits� of� the� word� address� are�

�internally� incremented.� The� high-order� ?ve� bits� of� the� address� remain� unchanged.�

�The� slave� acknowledges� the� reception� of� each� data� byte� with� an� ACK.� The� I� 2� C-bus�

�data� transfer� is� terminated� by� the� master� after� the� 8th� byte� with� a� STOP� condition.� If�

�the� master� transmits� more� than� eight� bytes� prior� to� generating� the� STOP� condition,�

�no� acknowledge� will� be� given� on� the� ninth� (and� following)� data� bytes� and� the� whole�

�transmission� will� be� ignored� and� no� programming� will� be� done.� As� in� the� byte� write�

�operation,� all� inputs� are� disabled� until� completion� of� the� internal� write� cycles.�

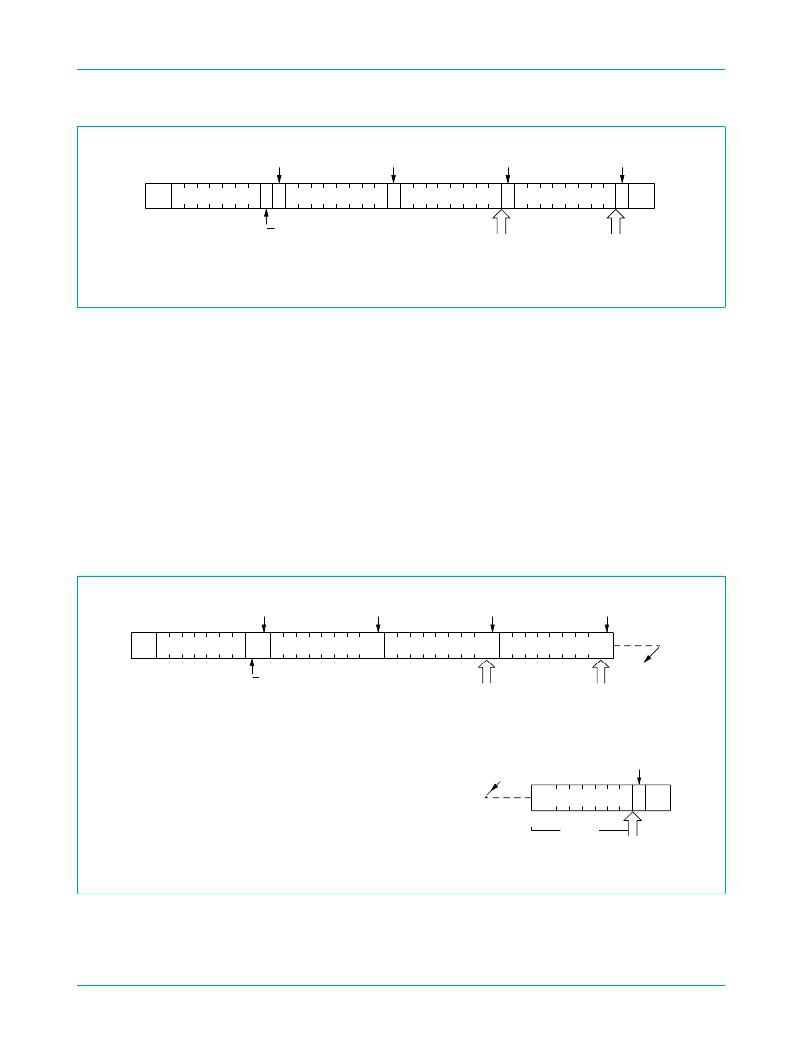

�acknowledge�

�from� slave�

�acknowledge�

�from� slave�

�acknowledge�

�from� slave�

�acknowledge�

�from� slave�

�S�

�SLAVE� ADDRESS�

�0� A�

�WORD� ADDRESS�

�A�

�DATA� N�

�A�

�DATA� N� +� 1�

�A�

�R/W�

�auto� increment�

�word� address�

�auto� increment�

�word� address�

�acknowledge�

�from� slave�

�DATA� N� +� 7�

�last� byte�

�A�

�A�

�Fig� 6.� Page� write� operation;� eight� bytes.�

�9397� 750� 14219�

�002aaa245�

�auto� increment�

�word� address�

�?� Koninklijke� Philips� Electronics� N.V.� 2004.� All� rights� reserved.�

�Product� data�

�Rev.� 06� —� 22� October� 2004�

�8� of� 21�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PCU9955TW,118

IC LED DRVR CONST CURR

PDA006B-700C

LED DRIVER 6W 700MA

PDA010B-700C

LED DRIVER 8.4W 700MA

PDA015B-350C

LED DRIVER 15W 350MA

PDA030B-700C

LED DRIVER 30W 700MA

PDC500-1024F

SINGLE OUTPUT 500W 24V

PDU1215

POWER STRIP 15A 13 OUT RACK M

PDU1220T

POWER STRIP 20A 13 OUT RACK MNT

相关代理商/技术参数

PCF8598C-2P02

制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:1024 ⅴ 8-bit CMOS EEPROM with I2C-bus interface

PCF8598C-2T

制造商:ICS 制造商全称:ICS 功能描述:PCF85xxC-2 family 256 to 1024 ⅴ 8-bit CMOS EEPROMs with I2C-bus interface

PCF8598C-2T/02,112

功能描述:电可擦除可编程只读存储器 8K/1024 电可擦除可编程只读存储器 I2C RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

PCF8598C-2T/02,118

功能描述:电可擦除可编程只读存储器 8K/1024 电可擦除可编程只读存储器 I2C BUS RoHS:否 制造商:Atmel 存储容量:2 Kbit 组织:256 B x 8 数据保留:100 yr 最大时钟频率:1000 KHz 最大工作电流:6 uA 工作电源电压:1.7 V to 5.5 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8

PCF8598C-2T02

制造商:PHILIPS 制造商全称:NXP Semiconductors 功能描述:1024 ⅴ 8-bit CMOS EEPROM with I2C-bus interface

PCF8598E-2P

制造商:未知厂家 制造商全称:未知厂家 功能描述:I2C Serial EEPROM

PCF8598E-2T

制造商:未知厂家 制造商全称:未知厂家 功能描述:I2C Serial EEPROM

PCF8598P

制造商:未知厂家 制造商全称:未知厂家 功能描述:I2C Serial EEPROM